- 您现在的位置:买卖IC网 > Sheet目录1997 > ICS8430S07AKILF (IDT, Integrated Device Technology Inc)IC CLK GENERATOR PLL 32VFQFN

ICS8430S07AKI REVISION A SEPTEMBER 3, 2009

16

2009 Integrated Device Technology, Inc.

ICS8430S07I Data Sheet

CLOCK GENERATOR FOR CAVIUM PROCESSORS

Termination for 3.3V LVPECL Outputs

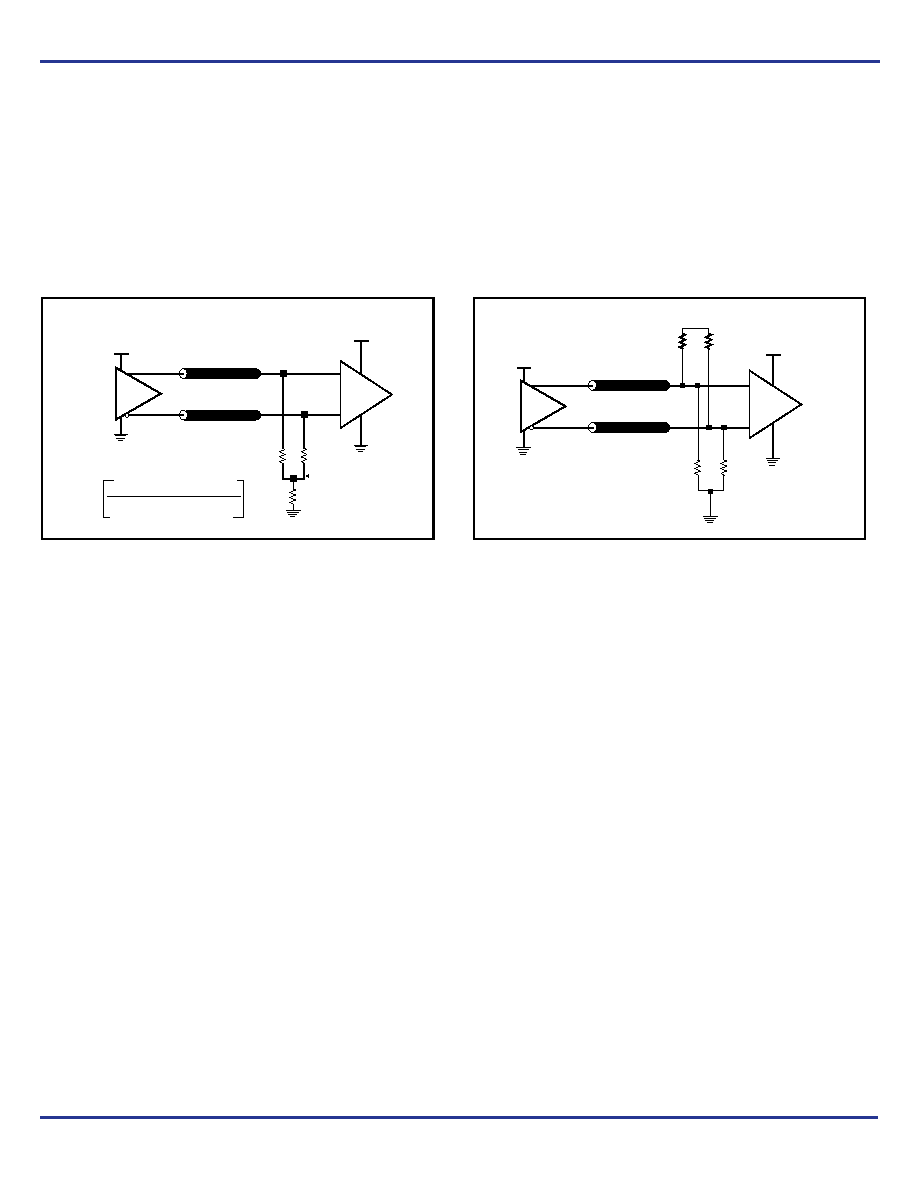

The clock layout topology shown below is a typical termination for

LVPECL outputs. The two different layouts mentioned are

recommended only as guidelines.

The differential output pair is low impedance follower outputs that

generate ECL/LVPECL compatible outputs. Therefore, terminating

resistors (DC current path to ground) or current sources must be

used for functionality. These outputs are designed to drive 50

transmission lines. Matched impedance techniques should be used

to maximize operating frequency and minimize signal distortion.

Figures 6A and 6B show two different layouts which are

recommended only as guidelines. Other suitable clock layouts may

exist and it would be recommended that the board designers

simulate to guarantee compatibility across all printed circuit and clock

component process variations.

Figure 6A. 3.3V LVPECL Output Termination

Figure 6B. 3.3V LVPECL Output Termination

3.3V

V

CC - 2V

R1

50

R2

50

RTT

Z

o = 50

Z

o = 50

+

_

RTT =

* Z

o

1

((V

OH + VOL) / (VCC – 2)) – 2

3.3V

LVPECL

Input

R1

84

R2

84

3.3V

R3

125

R4

125

Z

o = 50

Z

o = 50

LVPECL

Input

3.3V

+

_

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS8430S10BYI-02LF

IC CLK GENERATOR PLL 48TQFP

ICS84314AY-02LFT

IC SYNTHESIZER 700MHZ 32-LQFP

ICS843156AKILF

IC CLK GENERATOR 32VFQFP

ICS843156AKLF

IC CLK GENERATOR 32VFQFP

ICS843202AYILF

IC SYNTHESIZER 680MHZ 32-LQFP

ICS843204AGILF

IC SYNTHESIZER LVPECL 48-TSSOP

ICS84320AY-01LN

IC SYNTHESIZER GP LVPECL 32-LQFP

ICS84320AYI-01LF

IC FREQ SYNTHESIZER 32TQFP

相关代理商/技术参数

ICS8430S07AKILFT

功能描述:IC CLK GENERATOR PLL 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS8430S07I

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Clock Generator for Cavium Processors

ICS8430S10AYILF

功能描述:IC CLK GENERATOR PLL 48TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS8430S10AYILFT

功能描述:IC CLK GENERATOR PLL 48TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS8430S10BYI-02LF

功能描述:IC CLK GENERATOR PLL 48TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS8430S10BYI-02LFT

功能描述:IC CLK GENERATOR PLL 48TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS8430S10I-03

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Clock Generator for Cavium Processors

ICS8431-01

制造商:ICS 制造商全称:ICS 功能描述:200MHZ, LOW JITTER, LVPECL FREQUENCY SYNTHESIZER